You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

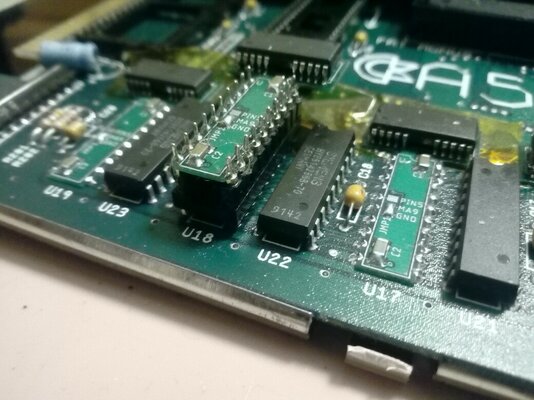

SOJ RAM to DIP-20 footprint adapters with 1M x 4 drams

- Thread starter mkl

- Start date

- Replies 5

- Views 1618

- Status

- Not open for further replies.

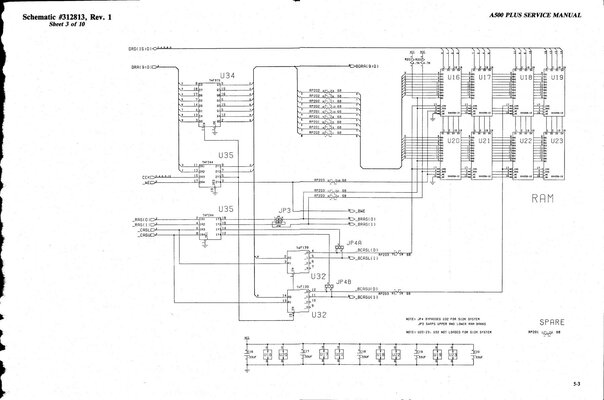

2Megs chip on rev8 A500+ mainboard with originally 512KB chip, 256K x4 dip-20 DRAM in U20..U23:

1. Wire connecting dram A9 on all 1M x 4 modules and to buffered BDRA9 on pin 2 on U34 74F373. A9 not connected to any mainboard dip-20 pad.

2. JP3 connections disconnected, leaving U20..23 *RAS pin inactive high R202 4.7K. *CAS signals will reach these chips still, probably with no effect.

3. No U32 74F139 installed. Jumpers 4A and 4B as "originally", connecting to U35 74F244 pins 12, 14 (buffered *casu, *casl)

4. Add AND-gate (1/4 of 74F08 or so) combines active low inputs *RAS0 and *RAS1 to output *RAS for U16..U19 1M x4 modules. Pin 4 (mainboard routing connects also to n.c. pin 5 for U16..U19))

4. inputs to and gate from U35 74F244 pins 2 and 4. Output to U16..U19 pin 4. (Or other end of R201, not the +5v VCC end.)

4B. Made AND gate from two schottky diodes and extra pull-up resistor, cathode -ends from U35 74F244 pins 16 and 18. +ends together to pin 2 of RP203. Resistor 270 Ohms added in parallel with R201 4.7Kohm.

5. Workbench showed 2 Megs graphics mem. Maybe works, but to be tested more.

1. Wire connecting dram A9 on all 1M x 4 modules and to buffered BDRA9 on pin 2 on U34 74F373. A9 not connected to any mainboard dip-20 pad.

2. JP3 connections disconnected, leaving U20..23 *RAS pin inactive high R202 4.7K. *CAS signals will reach these chips still, probably with no effect.

3. No U32 74F139 installed. Jumpers 4A and 4B as "originally", connecting to U35 74F244 pins 12, 14 (buffered *casu, *casl)

4. Add AND-gate (1/4 of 74F08 or so) combines active low inputs *RAS0 and *RAS1 to output *RAS for U16..U19 1M x4 modules. Pin 4 (mainboard routing connects also to n.c. pin 5 for U16..U19))

4. inputs to and gate from U35 74F244 pins 2 and 4. Output to U16..U19 pin 4. (Or other end of R201, not the +5v VCC end.)

4B. Made AND gate from two schottky diodes and extra pull-up resistor, cathode -ends from U35 74F244 pins 16 and 18. +ends together to pin 2 of RP203. Resistor 270 Ohms added in parallel with R201 4.7Kohm.

5. Workbench showed 2 Megs graphics mem. Maybe works, but to be tested more.

Last edited:

Eureka!. This may be the solution for many vxl 030 users, as there is no memory available se 1mx4 dip (at least I can't find it).

https://amiga.resource.cx/photos/vxl30,2

Do you have available 8mb (16 units of 1mgx4 chips)?.

https://amiga.resource.cx/photos/vxl30,2

Do you have available 8mb (16 units of 1mgx4 chips)?.

Last edited:

- Status

- Not open for further replies.