You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

A4000TX ATX Amiga motherboard

- Thread starter hese

- Start date

- Replies 695

- Views 213863

@hese: Regarding adding PCI - this is where it starts getting really interesting for me, upto now I didnt't see too much value-add given that I already own two real A4000T but was always eyeing towards a Mediator. What always kept me refrain from getting one was the will to keep the machines as close to original as possible. With a new board design in a new (PC) case I could perfectly imagine adding that to my collection. Great work!

Another idea is to copy the faster access of the cpu to chipram by using faster ram chips. This idea is proposed by the Amiga 1200 reloaded.

Last edited:

So so cool and so awesome you're considering PCI for rev 2. That will be the one I'm getting then

I saw this and was something I was thinking about too. But, was thinking a more inline slot. I've seen it on HP oem mobos for pci slots. It'd probably lead to other 3rd party expansions too.Or...

2, Can the Zorro connectors be be broken out and put on a daughter board? Making the board instead, So the mb will be a regular ATX board. And connected with a ribbon cable to the daughter board. That will also allow you to mount the cards in those vertical slots that cases now a days really like to have.

thebajaguy

Active member

I'd quote all the quotes, but go mad sorting things out, so just one:

Agreeing with this ;-)

I'd suggest leaving the needed signal points for the 64MB memory hack handy (TH machine pin). I have personally replaced the A3000's ZIP RAM socket zone with the 16MB DRAM PCB on machine pin headers, and honestly, a PCB that has the GAL (for the different memory matrix type, and/or additional addressing) and space for 64MB of SMC DRAM on it is the better solution if one is going to just max the memory and be done with it. When building such, one leaves the sockets off the motherboard and the 64MB (or larger) memory PCB is inserted into them and also to the (proposed) spare address lines. It can sit safely below any accelerator on simple machine pin header pins (soldered in). This would minimize the need to go additional layers, too.

I actually have an Ultrasound 060 in my A4KT, and it was purpose built for the medical project, and not general consumption, so no need to support. The CPU board has custom interface positions that extend forward of the motherboard by about 2"/4.5cm to make use of the native A4KT case's space. Unless one has that kind of forward clearance in their case of choice, it won't work as you have noted. The QuikPak 4060, unless the first Z3 slot has moved closer to the CPU area, should still work, or an overlap will happen.

I have found the publicly-available ROMY GAL and PCB online - you have to dig on Cosmo's site IIRC. Through a 3rd party, I was told Cosmos has made his money back for the efforts some time ago. Others have since made and sold the ROMY PCBs from what he eventually published (I have a small PCB run here for both A3000 and A4000, just haven't gotten around to built them).

The 1MB ROM (additional 512K at E0) is a safe hack to expand with. I caution the 4MB version because there is some back and forth about the upper address space's purpose in the memory map that it would sit at (>16MB), and a possible conflict. I won't debate who's right. Maybe leave the option open enough to someone that wants to program the GAL logic one way or the other. If not directly supported, leave the needed pins for the address line(s) nearby so a riser PCB can inserted in directly so one doesn't have to put an inverted socket on an SMC Amiga chip.

Item to add: A jumper nearby for enable/disable pin-20 power for an IDE DOM (or self-powered CF adapter) on the IDE header. My HC533 and the IDE68K support power from the pin-20, but the A4KT doesn't. I like to use the Hyperdisk IDE DOM modules, and they support it. I've also debated putting in a 90-degree IDE header so a module can lay flat vs vertical. Inward won't work due to the ROMs on the official A4K, but outward would.

I agree that enough space for SMC GAL sockets to fit would be nice for the most likely GAL change-outs. Putting as many passives as possible on the back side is also a suggestion. Makes for a cleaner PCB to read any needed silkscreen writing. One could argue that it might be possible to get the rear side built by the PCB house fitted with passives. This would reduce the labor-intensive effort of the tiny parts to just 74-series logic, connectors, and Amiga chip additions by the purchaser on the top side.

Thanks for all of your efforts, which ever way you decide to go.

Wow, so many replies

Harkonnen75 said:It is necessary to clone hese. I propose to do a crowfounding to replicate hese!

Lolz :laugh:

I have so many projects that I'd like to do (some of them are already progressing) and so little time...

Agreeing with this ;-)

I'd suggest leaving the needed signal points for the 64MB memory hack handy (TH machine pin). I have personally replaced the A3000's ZIP RAM socket zone with the 16MB DRAM PCB on machine pin headers, and honestly, a PCB that has the GAL (for the different memory matrix type, and/or additional addressing) and space for 64MB of SMC DRAM on it is the better solution if one is going to just max the memory and be done with it. When building such, one leaves the sockets off the motherboard and the 64MB (or larger) memory PCB is inserted into them and also to the (proposed) spare address lines. It can sit safely below any accelerator on simple machine pin header pins (soldered in). This would minimize the need to go additional layers, too.

I actually have an Ultrasound 060 in my A4KT, and it was purpose built for the medical project, and not general consumption, so no need to support. The CPU board has custom interface positions that extend forward of the motherboard by about 2"/4.5cm to make use of the native A4KT case's space. Unless one has that kind of forward clearance in their case of choice, it won't work as you have noted. The QuikPak 4060, unless the first Z3 slot has moved closer to the CPU area, should still work, or an overlap will happen.

I have found the publicly-available ROMY GAL and PCB online - you have to dig on Cosmo's site IIRC. Through a 3rd party, I was told Cosmos has made his money back for the efforts some time ago. Others have since made and sold the ROMY PCBs from what he eventually published (I have a small PCB run here for both A3000 and A4000, just haven't gotten around to built them).

The 1MB ROM (additional 512K at E0) is a safe hack to expand with. I caution the 4MB version because there is some back and forth about the upper address space's purpose in the memory map that it would sit at (>16MB), and a possible conflict. I won't debate who's right. Maybe leave the option open enough to someone that wants to program the GAL logic one way or the other. If not directly supported, leave the needed pins for the address line(s) nearby so a riser PCB can inserted in directly so one doesn't have to put an inverted socket on an SMC Amiga chip.

Item to add: A jumper nearby for enable/disable pin-20 power for an IDE DOM (or self-powered CF adapter) on the IDE header. My HC533 and the IDE68K support power from the pin-20, but the A4KT doesn't. I like to use the Hyperdisk IDE DOM modules, and they support it. I've also debated putting in a 90-degree IDE header so a module can lay flat vs vertical. Inward won't work due to the ROMs on the official A4K, but outward would.

I agree that enough space for SMC GAL sockets to fit would be nice for the most likely GAL change-outs. Putting as many passives as possible on the back side is also a suggestion. Makes for a cleaner PCB to read any needed silkscreen writing. One could argue that it might be possible to get the rear side built by the PCB house fitted with passives. This would reduce the labor-intensive effort of the tiny parts to just 74-series logic, connectors, and Amiga chip additions by the purchaser on the top side.

Thanks for all of your efforts, which ever way you decide to go.

Last edited:

Great work Hese!

Fantastic project hese! Sign me up for one!

Fantastic project hese! Sign me up for one!A couple of thoughts on "extras" to include:

- I'd like a Ratte monitor switch embedded - they are difficult to get hold of but invaluable when you have RTG

- On PCI, I'd vote for an embedded Mediator not Prometheus. I say this because there is a lot of work going on to support PPC cards via PCI on the Mediator, including relatively cheap NIC cards (see EAB thread on this). Having the Mediator built in makes this kind of thing easier to implement. I realise the Mediator isn't open source though so could be tough to achieve.

I realise the Mediator isn't open source though so could be tough to achieve.

Good Idea's Wrangler,

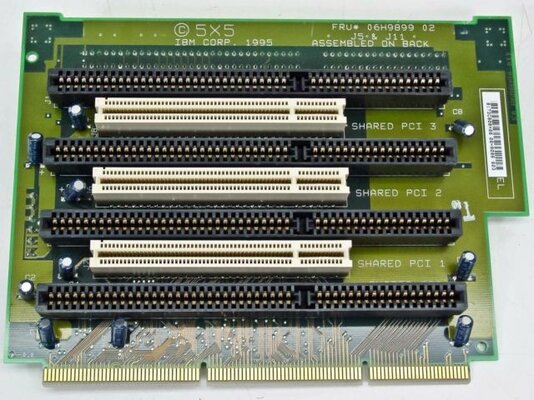

I'm no electronics engineer but wouldn't hese just have to have a Zorro slot inline with a PCI slot and then you would fit one of these,

http://eu-shop.elbox.com/en_GB/p/Mediator-PCI-4000-MK-III-MM-CD/646

This would give access to say maybe having PCI slots fitted in place of the ISA Slots?

This could be another version of the board maybe because there will be some users out there who would also like to utilise the ISA slots fitted to his current design

I'm no electronics engineer but wouldn't hese just have to have a Zorro slot inline with a PCI slot and then you would fit one of these,

View attachment 139162

Yeah, good idea!

This is really impressive I will wan't one when PCI is added. I can then just use the Elbox logic board.

Also if you add Meutoxo's 112MB Mod, you could drop two of the SIMM sockets freeing up a bit more space for another Zorro Slot.

Also if you add Meutoxo's 112MB Mod, you could drop two of the SIMM sockets freeing up a bit more space for another Zorro Slot.

Last edited:

Two nights ago, I dreamt I had it XD

Last edited:

I have been fully occupied with other things the last few weeks and haven't had much time to work on this.

Nevertheless, here is a snapshot of the production board (rev1.1) that I'm working on.

The rev1.1 will have support for 2MB/4MB Kickstart (Romy), PC floppy drives (Stedy) and some extra fans. No much space left to add more features, so probably all the other good stuff (PCI Mediator/Prometheus/both?, USB ports, USB input devices, more Fast RAM, ...) will have to wait till rev 2.0.

- - - Updated - - -

Nevertheless, here is a snapshot of the production board (rev1.1) that I'm working on.

The rev1.1 will have support for 2MB/4MB Kickstart (Romy), PC floppy drives (Stedy) and some extra fans. No much space left to add more features, so probably all the other good stuff (PCI Mediator/Prometheus/both?, USB ports, USB input devices, more Fast RAM, ...) will have to wait till rev 2.0.

- - - Updated - - -

Yes.Will there be a collective order for these boards ?

Similar threads

- Replies

- 2

- Views

- 417

- Replies

- 0

- Views

- 407

- Locked

- Replies

- 16

- Views

- 1K

- Locked

- Replies

- 9

- Views

- 1K